Данное руководство основано на следующих:

instructables.com, xilinx-wiki.atlassian.net, github.com.

Разработка FPGA части будет производиться в Vivado 2019.1, компиляция необходимых файлов для Linux будет выполнена в виртуальной машине Oracle VM VirtualBox, на которой установлена Ubuntu.

Компиляция будет происходить без использования PetaLinux, как утверждают Xilinx - это платформа, которая содержит всё необходимое для запуска Linux на FPGA и облегчает внесение изменений. В данном руководстве всё будет собираться ручным образом, для того чтобы ближе взглянуть на работу встроенных систем.

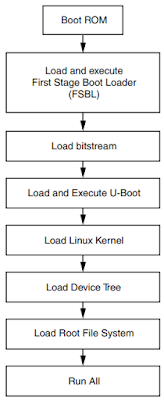

Процесс загрузки системы описывается следующей схемой, взятой из UG1165 и UG873:

|

| Рис.1 структурная схема загрузки системы |

Boot ROM - выполнение инструкций содержащихся в специально отведённой памяти FPGA, они осуществляют изначальную инициализацию, выбирают носитель в котором будет произведён поиск FSBL и запускают его. Изменить этот код нельзя, остальные файлы необходимо подготовить.

Итак начнём.

Первым шагом следует создать проект в Vivado. Для проверки работоспособности платы и корректных настроек можно использовать готовый проект от Xilinx расположенный на github, он реализован на версии 2017.4. Но в данном руководстве используется версия 2019.1 и проект создаётся с нуля. Тем не менее там можно посмотреть правильные настройки для DDR и QSPI.

В отладочной плате Zybo используется XC7Z010CLG400С-1 его и следует выбрать при создании проекта. Xilinx рекомендует использовать готовые библиотеки для своих отладочных плат, при создании проекта, вместо конкретной микросхемы. Как они говорят это облегчает подключение различных интерфейсов, подробное описание здесь. Но для того чтобы не привязываться к конкретным библиотекам выберем отдельно необходимую микросхему.

|

| Рис.2 Выбор микросхемы |

После этого нужно соединить выводы FCLK_CLK0 и M_AXI_GP0_ACLK, таким образом подаётся частота на AXI интерфейс, он использоваться не будет, но без этого нельзя скомпилировать проект.

|

| Рис.3 IP ядро процессора |

Подключение и используемые компоненты можно посмотреть на схеме, которая находится в открытом доступе.

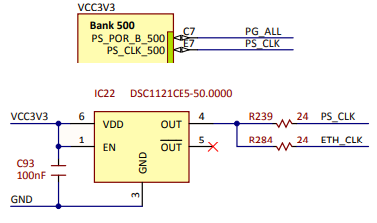

Двойным щелчком можно открыть настройки IP ядра процессора, для начала в разделе "Clock configuration" выставим корректное значение тактовой частоты процессора. Тактовые сигналы подаются на вывод PS_CLK_500, его и к чему он подсоединяется можно найти на странице 9:

|

| Рис.4 Генератор тактовой частоты процессора |

Выставим это в Vivado:

|

| Рис.5 Настройка тактовой частоты процессора |

|

| Рис.6 RAM память |

|

| Рис.7 Настройка RAM |

|

| Рис.8 Настройка задержек на дорожках печатной платы |

|

| Рис.9 Настройка интерфейсов |

|

| Рис.10 Настройка интерфейсов (2) |

|

| Рис.11 Настройка интерфейсов (3) |

|

| Рис.12 Настройка интерфейсов (3) |

После этого нужно скомпилировать проект. Затем экспортировать его в SDK, нажав File -> Export -> Hardware. В появившемся окне нужно поставить галочку рядом с "Include bitstream" и нажать ок.

Последним шагом следует запустить SDK через File -> Launch SDK. В дальнейшем в Vivado вводить изменения больше не потребуется.

Внутри SDK, нужно создать FSBL. Он установит правильные настройки частоты и DDR вместе с QSPI. Также загрузит все файлы в RAM. Дополнительная информация: Видео от Xilinx про FSBL. Xilinx wiki FSBL, документация TRM UG585, UG821. Для этого следует создать новый проект File -> New -> Application project.

|

| Рис.13 Создание нового проекта |

|

| Рис.14 Выбор FSBL |

Далее большая часть работы будет происходить в Linux. Также нужно будет переносить файлы между двумя ОС, как это делать в Oracle VM описано здесь.

Все необходимые файлы можно найти на xilinx-wiki.atlassian.net.

Дополнительная информация про U-Boot и про компиляцию: Build U-Boot.

Проще всего скачивать файлы через Git, для того чтобы его установить нужно выполнить:

sudo apt-get install git-core

U-Boot

git clone https://github.com/Xilinx/u-boot-xlnx.git

После этого в домашней директории появится папка u-boot-xlnx

Необходимо перейти в неё и запустить там командную строку.

cd u-boot-xlnx

Далее выполнить следующие команды

export CROSS_COMPILE=arm-linux-gnueabihf-

export ARCH=arm

make zynq_zybo_config

Если терминал выдаст следующие ошибки:

YACC scripts/kconfig/zconf.tab.c

/bin/sh: 1: bison: not found

scripts/Makefile.lib:228: recipe for target 'scripts/kconfig/zconf.tab.c' failed

make[1]: *** [scripts/kconfig/zconf.tab.c] Error 127

Makefile:496: recipe for target 'zynq_zybo_config' failed

make: *** [zynq_zybo_config] Error 2

То необходимо установить пакет bison:

sudo apt-get install bison

и попробовать ещё раз. Успешно выполненная команда выглядит следующим образом:

|

| Рис.15 конфигурация U-Boot |

После конфигурации необходимо выполнить команду

make

Это скомпилирует U-Boot, создаст файл U-Boot.elf в той же директории и утилиту mkimage которые будут использованы в дальнейшем.

Linux

Следующим шагом скомпилируем ядро Linux. Подробнее об этом xilinx-wiki.atlassian.net. Сперва скачаем его используя команду:

git clone https://github.com/Xilinx/linux-xlnx.git

Переходим в созданную директорию:

cd linux-xlnx

Настраиваем ядро:

make ARCH=arm xilinx_zynq_defconfig

make ARCH=arm menuconfig

Откроется меню настроек, если вам не нужны дополнительные изменения, можно просто закрыть окно:

|

| Рис.16 Конфигурация Linux |

Запускаем компиляцию командой

make ARCH=arm UIMAGE_LOADADDR=0x8000 uImage

Если вылезет ошибка:

gcc: error: unrecognized argument in option ‘-mabi=aapcs-linux’

необходимо заново выполнить следующую команду:

export CROSS_COMPILE=arm-linux-gnueabihf-

После компиляции в папке

linux-xlnx/arch/arm/boot

появится файл

uImage

Это и есть скомпилированное ядро.

DTB

Нужно использовать DTB файл, который называется "Device tree". Он описывает Linux какое железо используется, подробнее об этом здесь.

Он уже скомпилированный находится в папке

/u-boot-xlnx/arch/arm/dts/

под названием

zynq-zybo.dtb

Но ради практики скомпилируем новый файл, это делается следующими командами:

cd u-boot-xlnx

./scripts/dtc/dtc -I dts -O dtb -o ./devicetree.dtb ./arch/arm/dts/zynq-zybo.dts

Если вылезет ошибка:

Error: ./arch/arm/dts/zynq-zybo.dts:7.1-9 syntax error

FATAL ERROR: Unable to parse input tree

Необходимо в dts файле изменить строчку

#include "zynq-7000.dtsi"

на

/include/ "zynq-7000.dtsi"

Терминал не должен ничего вывести при успешном выполнении:

|

| Рис.17 Компиляция device tree |

Если всё вышло корректно, должен появится devicetree.dtb файл в папке u-boot-xlnx.

Root File System

Теперь нужно создать файловую систему с которой будет работать Linux, при создании U-boot, также была создана утилита для создания файловой системы.

Сперва нужно скачать файл arm_ramdisk.image.gz, на этой странице также находится более подробное описание данного шага.

Но всё же, если скачанный файл находится в папке Downloads, то из корневой директории необходимо выполнить:

./u-boot-xlnx/tools/mkimage -A arm -T ramdisk -C gzip -d ./Downloads/arm_ramdisk.image.gz uramdisk.image.gz

При успешном выполнении в корневой директории появится файл uramdisk.image.gz который понадобится в дальнейшем.

BOOT image

Теперь необходимо соединить все файлы вместе и создать загрузочный файл для QSPI. После переноса файлов из Linux в Windows, возвращаемся в SDK и выполняем следующее:

Xilinx -> Create Boot Image

Необходимо добавить все созданные файлы, .bit файл FPGA не обязателен, если нам нужен только процессор. Для всех файлов кроме FSBL, .BIT и U-Boot необходимо указать их расположение в памяти, для этого при добавлении файла ему присваивается offset. По умолчанию при запуске U-Boot с QSPI, адреса следующие: uImage = 0x100000, devicetree = 0x600000, uramdisk.image.gz = 0x620000. Если их указать некорректно, то в терминале будет показана ошибка и корректный адрес. Также их можно посмотреть или изменить в исходниках U-Boot include/configs/zynq-common.h после

"qspiboot=run xilinxcmd && " \

Либо в руководстве к ZC702.

Необходимо добавить все созданные файлы, .bit файл FPGA не обязателен, если нам нужен только процессор. Для всех файлов кроме FSBL, .BIT и U-Boot необходимо указать их расположение в памяти, для этого при добавлении файла ему присваивается offset. По умолчанию при запуске U-Boot с QSPI, адреса следующие: uImage = 0x100000, devicetree = 0x600000, uramdisk.image.gz = 0x620000. Если их указать некорректно, то в терминале будет показана ошибка и корректный адрес. Также их можно посмотреть или изменить в исходниках U-Boot include/configs/zynq-common.h после

"qspiboot=run xilinxcmd && " \

Либо в руководстве к ZC702.

Также файлы должны быть расположены в правильном порядке, по моменту запуска, в памяти они располагаются друг за другом. Для FSBL в графе Partition type вместо datafile нужно поставить bootloader, в результате должно выглядеть примерно так:

|

| Рис.19 Добавление смещения |

Для программирования QSPI, нужно выбрать Xilinx -> Programm Flash. В появившемся окне добавить BOOT.bin в Image File и FSBL:

|

| Рис.20 Программирование QSPI |

При программировании Zybo следует перевести в режим JTAG. После успешного программирования, плату следует перевести в режим загрузки с QSPI и включить, через terminal подключившись к COM порту, можно следить за выполнением загрузки Linux и в дальнейшем с ним работать.

Здравствуйте!

ОтветитьУдалитьУстановил Vivado 2019.2. В данной версии нет SDK. Как теперь быть?

Может есть какие-то костыли или что-то ещё подскажете?

Vladimir035

ОтветитьУдалитьЗдравствуйте. Начиная с версии 2019.2 Vivado является частью среды Vitis.

Vitis в свою очередь теперь заменяет SDK.

В общем с версии 2019.2 SDK выпилили.

Благодарю автора статьи за такое детальное изложение материала и попутные комментарии.

Спасибо, за статью!!

ОтветитьУдалитьИзрядно сэкономила время.